## Design of a high voltage charge pump in advanced CMOS

Haowei Bi Student number: 02102021

Supervisors: Prof. dr. ir. Johan Bauwelinck, Prof. dr. ir. Guy Torfs Counsellors: Achim Vandierendonck, Xin Wang

Master's dissertation submitted in order to obtain the academic degree of Master of Science in Electrical Engineering - main subject Electronic Circuits and Systems

Academic year 2022-2023

This page is intentionally left blank.

### Acknowledgements

After six years of studying electrical engineering, my student career is coming to an end. Over the past year, through this project, I have gained a lot, which would not have been possible without the help and guidance of many people.

I would like to express my special gratitude to Prof. dr. ir. Guy Torfs and Prof. dr. ir. Johan Bauwelinck, my promotors, for providing me with the opportunity to research fascinating charge pumps and for their guidance in my classes throughout the past two years. Professor Bauwelinck always wears a friendly smile, making him approachable. Professor Torfs's intelligence often makes me feel stupid. But after all he is a professor while I am just an inexperienced graduate student. The guidance from both professors has enriched my graduate studies significantly.

I would also like to extend special thanks to Xin Wang, my supervisor. Xin's expertise and solid foundation in the field make him a researcher whom I deeply admire. Throughout the past year, I have consistently sought the expertise and guidance of Xin, who has consistently exhibited exemplary professionalism and dedication in addressing my numerous inquiries. Xin's unwavering patience and meticulousness in providing comprehensive answers have been truly commendable, with a notable commitment to ensuring my understanding and satisfaction with each response. I am particularly grateful for Xin's willingness to extend his support beyond regular working hours, as he has willingly accommodated my queries even during late evenings, surpassing expectations and displaying a remarkable level of dedication. Xin's commitment to excellence and exceptional service has made a significant impact on my experience, and I sincerely appreciate the valuable assistance received throughout our interactions. His guidance has transformed me from someone with no knowledge to someone with a deep understanding of charge pumps, gradually developing a fondness for circuit research. Xin not only imparted knowledge but also taught me how to approach problems. Initially, I had no idea how to analyze simulation results, but now, although my analytical skills are still relatively weak, I often know where to start and what results to expect. Additionally, Xin has provided me with invaluable support in my personal life. Over the past six months, as I searched for employment, Xin recommended many companies and offered me valuable job advice. Every conversation with Xin provided comfort during times of high stress. Xin made my past year of study fulfilling and prevented me from feeling lost. In my heart, Xin is not just a teacher; he embodies the true meaning of "imparting knowledge and dispelling doubts." Words cannot fully express my gratitude, and I wish Xin all the best in the future.

I would also like to express my special gratitude to Achim Vandierendonck. Since our first encounter at OpenLab, I have found him to be a warm-hearted person. He always speaks slowly and patiently explains things to me multiple times. Whenever I had professional questions, he provided clear and concise answers. I also wish Achim all the best.

From the moment I decided to study on the other side of the Earth, over 8,000 kilometers away from home, to now, as I prepare to leave this place that always seems to rain, almost two years have passed. Leaving my comfort zone and arriving in a place with a different language and culture was undoubtedly a challenging journey. Throughout the past two years, I have often felt a sense of loneliness, and I am grateful for the companionship of my friends.

I would like to thank my boyfriend, Yiqi Wang. I appreciate him for preparing delicious food for me every day last year and teaching me how to cook before he returned to China. He patiently listens to me every day, doubling my happiness during joyful moments and sharing my sorrows during moments of despair.

I would also like to express my gratitude to my best friend, Zhexuan Liu . Although it has been a long time since we last met in person, and we can only communicate online, Zhexuan always provides endless encouragement and comfort. Every day, I feel loved because of Zhexuan, and I am thankful for the happiness she brings me.

Additionally, I want to thank my friends studying in Ugent for making the arduous process of writing my thesis feel less lonely, for sharing delicious meals that made me feel like I was back home.

I would also like to thank my families for their support in providing me with the opportunity to pursue my education without any financial burden.

Lastly, I want to extend my deepest gratitude to myself. My academic journey in Belgium has presented a multitude of challenges, both on a personal and societal level. The arduous process of assimilating into a foreign culture, coupled with unfavorable weather conditions, has consistently weighed heavily on my daily experiences, often leading to emotional distress. However, despite the adversity encountered, I have remained steadfast in my pursuit of personal and academic growth, ultimately transforming these two years into profoundly valuable and cherished memories. I appreciate the countless hours of hard work I have dedicated to my studies, as well as my optimistic mindset that has carried me through numerous challenges without giving up. I hope that the path ahead becomes even smoother!

Haowei Bi, May 2023

### Admission to loan

"The author(s) gives (give) permission to make this master dissertation available for consultation and to copy parts of this master's dissertation for personal use. In the case of any other use, the copyright terms have to be respected, in particular with regard to the obligation to state expressly the source when quoting results from this master dissertation."

### Toegang tot bruikleen

"De auteur(s) geeft (geven) de toelating dit afstudeerwerk voor consultatie beschikbaar te stellen en delen van het afstudeerwerk te kopiëren voor persoonlijk gebruik. Elk ander gebruik valt onder de beperkingen van het auteursrecht, in het bijzonder met betrekking tot de verplichting de bron uitdrukkelijk te vermelden bij het aanhalen van resultaten uit dit afstudeerwerk."

Haowei Bi, May 2023

This page is intentionally left blank.

### Design of a high voltage charge pump in advanced CMOS

by

HAOWEI BI

Master's dissertation submitted in order to obtain the academic degree of Master of Science in Electrical Engineering

Supervisor: Prof. dr. ir. Guy Torfs, Prof. dr. ir. Johan Bauwelinck Counsellor: Xin Wang & Achim Vandierendonck

> Faculty of Engineering and Architecture Ghent University

Department of Information Technology Chair: Prof. dr. ir. Bart Dhoedt

Abstract - With the increasing demand for high voltage in electronic systems, such as sensor systems, communication devices like RF amplifiers and power amplifiers, as well as MEMS systems, the need for chip-level high-voltage design that is compact and efficient has become essential. This paper presents the design of charge pump circuits to achieve a high voltage of 20 V from a 1.8 V voltage supply for chip-level applications. Given the high integration requirements, the primary focus is to minimize the area and enhance power efficiency. The main challenge lies in the limitation imposed by the breakdown voltage of MOS transistors. This study investigates the fundamental principles of charge pumps and explores the design parameters, including output voltage, ripple, settling time, and power consumption. Dickson charge pump is designed firstly. To overcome the limitations imposed by threshold voltage in the Dickson charge pump output, a charge pump structure utilizing charge transfer switches is studied. Ultimately, the design achieves an efficiency of 71.15% with a 25-stage charge pump structure, operating at a frequency of 100 kHz and a load current of 1 uA.

Keywords - High voltage on chip, Charge pump, Dickson CP, Dynamic CTS's

This page is intentionally left blank.

### Design of a high voltage charge pump in advanced CMOS

Haowei Bi Prof. dr. ir. Guy Torfs, Prof. dr. ir. Johan Bauwelinck Xin Wang & Achim Vandierendonck *Ghent University*

Abstract—With the increasing demand for high voltage in electronic systems, the need for chip-level high-voltage design that is compact and efficient has become essential. This paper presents the design of a charge pump circuit to achieve a high voltage of 20 V from a 1.8 V power supply for chip-level applications. This study investigates the fundamental principles of charge pumps and explores the design parameters, including output voltage, ripple, settling time, and power consumption. Starting with the Dickson charge pump, circuits utilizing charge transfer switch(CTS's) are also discussed. Ultimately, the design achieves an efficiency of 71.15% with a 25-stage charge pump, operating at a frequency of  $100 \, \mathrm{kHz}$  and a load current of  $1 \, \mathrm{uA}$ .

Index Terms—High voltage on chip, Charge pump, Dickson CP, Dynamic CTS's

### I. INTRODUCTION

In MEMS systems, high voltage is needed to drive specific variable capacitors for improved linearity and reduced phase noise [1]. Generally, external power supplies, boost Chopper, charge pump can be used for generating high voltage.

Given the need for higher integration density and lower power consumption, both the channel length and supply voltage of CMOS are becoming increasingly smaller.the application of charge pumps has become increasingly widespread.

Section II introduces general design considerations of charge pump. Section III and section IV provide a specific design of the Dickson charge pump and CTS's charge pump. Finally, a comparative analysis is conducted between the two topology structures.

#### II. DICKSON CHARGE PUMP

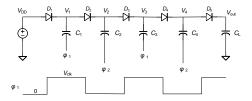

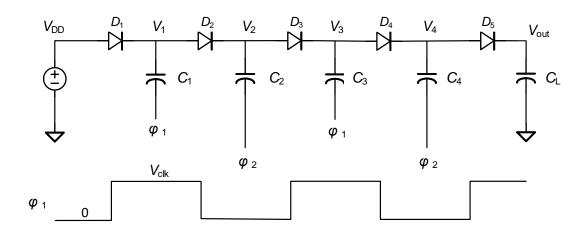

In [2], the principle of Dickson charge pump is introduced. Fig. 1 indicates the schematic of a four-stage Dickson charge pump.

Fig. 1: Schematic of 4-stage Dickson charge pump without loading

When designing a 4-stage charge pump, various factors need to be considered when selecting each component, such as output voltage, ripple, power efficiency, and so on. Each of these factors will be discussed in detail in this section.

### A. Output voltage

As charge is transferred from the voltage source in a stepby-step manner, so the voltage increases incrementally before reaching a steady state and increases stage by stage. For a N-stage charge pump, assume MOSFET size limitations on load current and parasitic capacitance are ignored, the output voltage can be expressed as:

$$V_{out} = V_{DD} + N \cdot \Delta V - (N+1) \cdot V_{th} \tag{1}$$

$$\Delta V = V_{clk} \cdot C_i - \frac{I_o}{f \cdot C_i} \tag{2}$$

where  $V_{clk}$  is the high voltage of the clock pulse,  $C_i$  is the capacitor in each stage,  $I_o$  is the loading current and f is the frequency of clock pulse. If the limitation of the MOSFET size is considered, a term related to the load current needs to be subtracted from the expression of  $\Delta V$ .

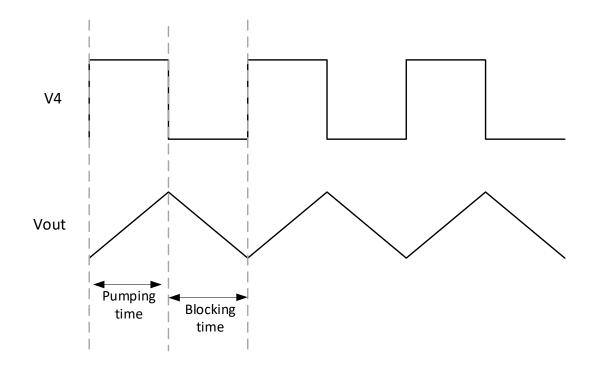

### B. Ripple

Ripple is generated by the charging and discharging process of  $C_L$  due to the period change of clock signals. In pumping time, the output capacitor is charged by the capacitor  $C_N$ , so  $V_{out}$  goes up. In blocking time, the output capacitor is discharged by the loading current, so the  $V_{out}$  goes down. The ripple of the output voltage is given by

$$Rippple = \frac{I_o \cdot \Delta t}{C_L} = \frac{I_o}{2 \cdot f \cdot C_L} \tag{3}$$

where  $\Delta t$  is time of charging or discharging, and  $C_L$  is the output capacitor.

#### C. Power consumption

For a realistic charge pump circuit, power current consists of the current consumption in a ideal charge pump at steady stage and power current due to parasitic effects. The ratio of output power over input power is used to calculated the power efficiency:

$$\eta = \frac{P_{out}}{P_{in}} = \frac{V_{out} \cdot I_o}{V_{DD} \cdot I_{in} + V_{clk} \cdot I_b} \tag{4}$$

where  $I_b$  is the current flowing through buffer.

#### III. DESIGN OF DICKSON CHARGE PUMP

### A. Switch design

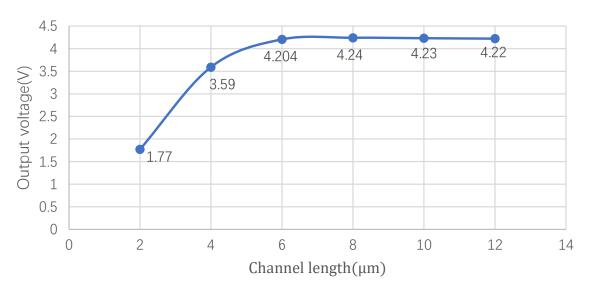

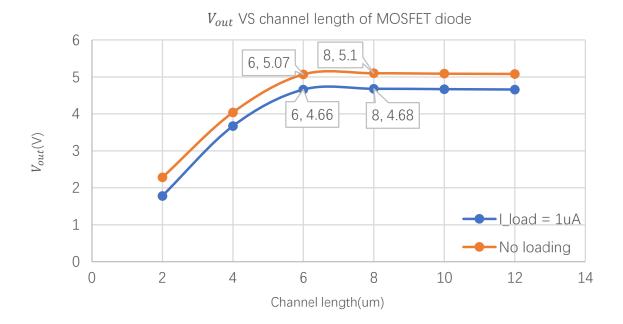

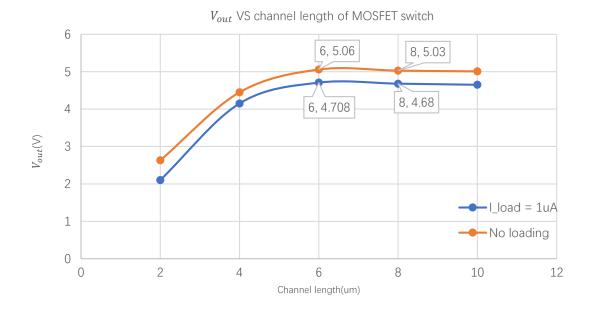

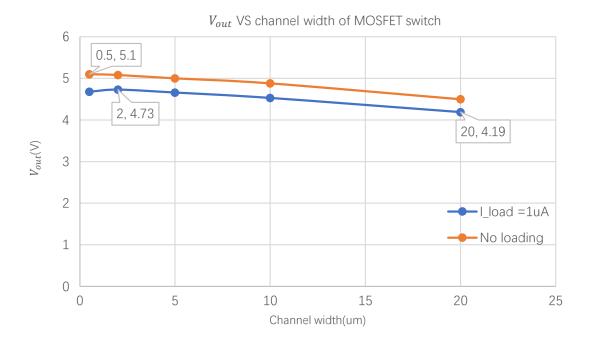

Transistor with smaller channel length experiences worse short channel effect and gives larger leakage current, resulting in a larger voltage drop at the output of the switch. Therefore, it is necessary to increase the channel length. Taking into account the trade-off between area and output voltage, ultimately, a channel length value of 6 um is chosen.

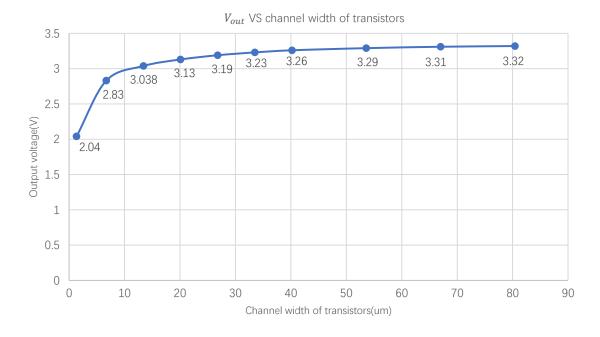

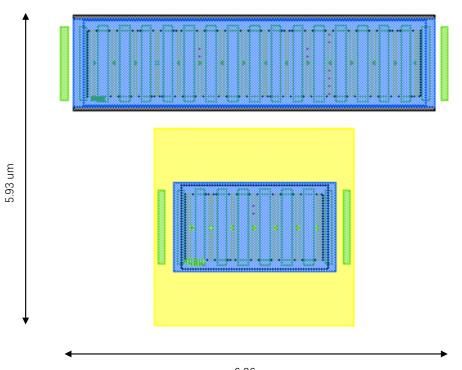

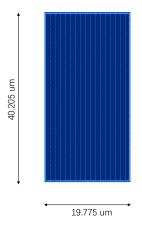

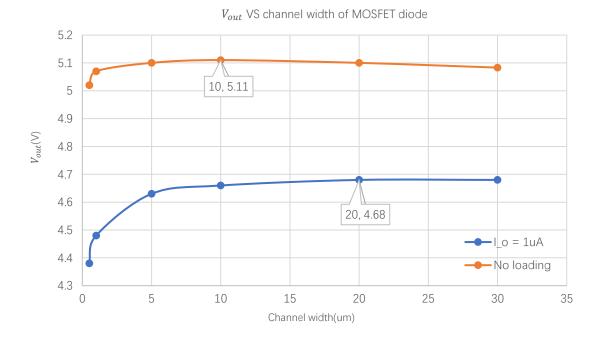

For designing the channel width, when a 1 uA loading current is added, the voltage between gate terminal and source terminal  $V_{GS}$  is large when size of transistor is small, which leads to incompletely charging of  $V_1$ . Considering that increasing the transistor size results in larger occupied area, the W/L value of 40.3 um / 6 um is chosen.

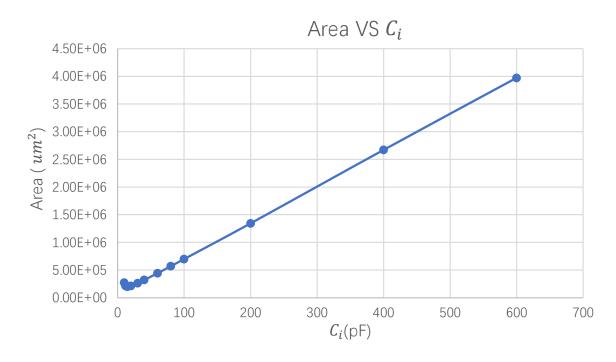

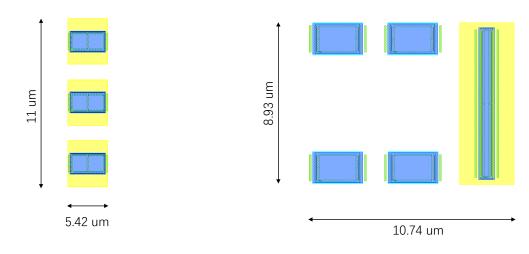

### B. Area limitation

In the design of a charge pump, the area occupied by the circuit is also an important consideration. For a  $60 \,\mathrm{pF}$ capacitor, it occupies an area of  $10\,706\,\mathrm{um^2}$  with a capacitance density denoted as  $5.604\,\mathrm{fF}/\mathrm{um^2}$ , which is much larger than the total area of transistor and buffer  $1127.902\,\mathrm{um^2}$ . So the area of circuit can be approximated as the area of capacitors:

$$Area = (NC_i + C_L) \cdot C_{density} \tag{5}$$

### C. Capacitance size choice

#### a) Capacitance in each stage

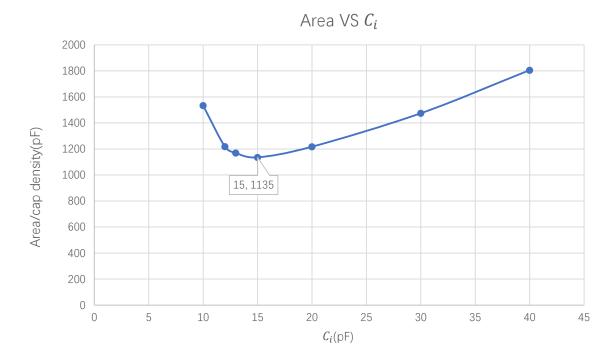

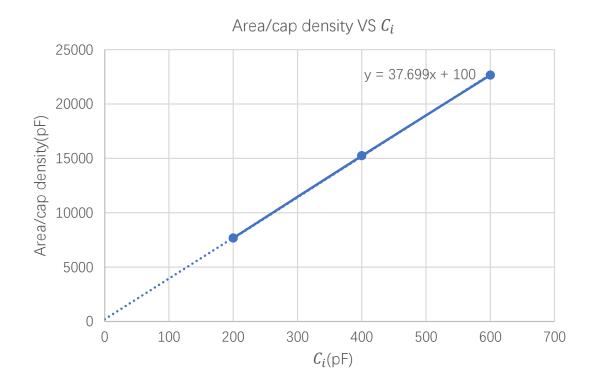

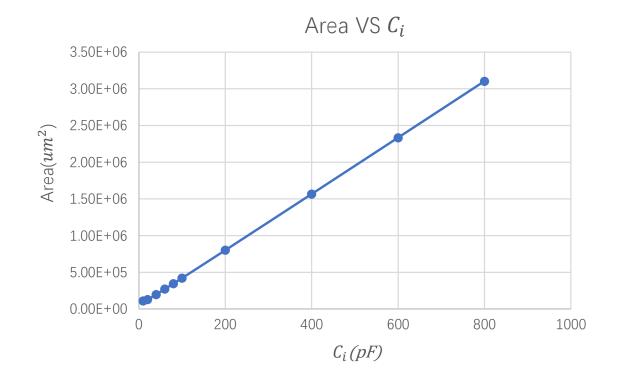

The selection of capacitance value is primarily considered from two aspects: area and efficiency.

Small value of  $C_i$  means more stages and large value of  $C_i$  means larger area for each stage. The optimal value of capacitance is 15 pF, occupying an area of 203 0.203 mm<sup>2</sup>.

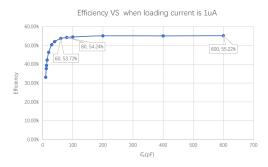

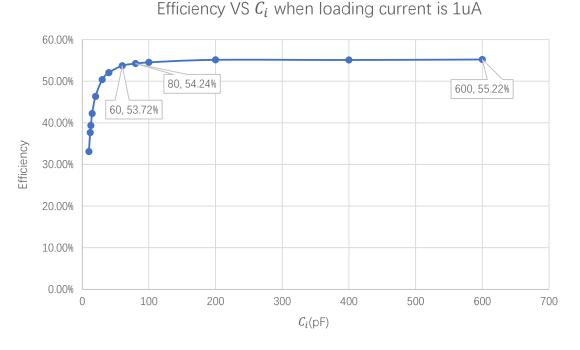

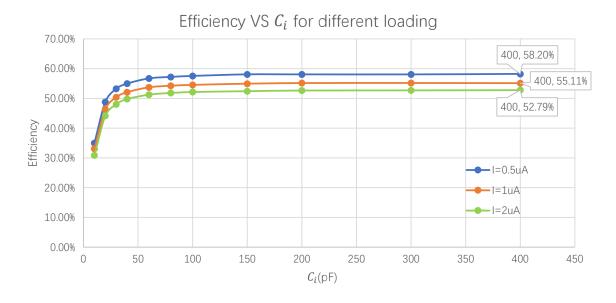

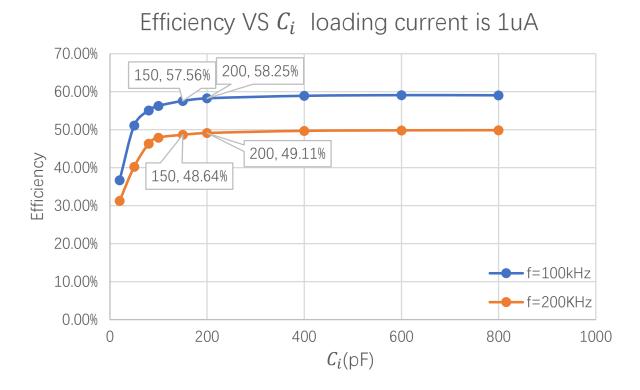

For efficiency, small capacitance leads to small output voltage according to Equation 1 and Equation 2, which cause small efficiency. While capacitance reaches a certain value, continuing to increase capacitance will not significantly increase  $V_{out}$ , so the efficiency is almost unchanged when the capacitance is large. As can be seen in Fig. 2 that When

Fig. 2: Efficiency VS  $C_i$  when  $I_o$  is 1  $\mu$  A

the capacitance is  $60 \,\mathrm{pF}$ , the efficiency is 53.72%, which has almost reached its maximum value for the given load. Therefore, when the load is  $1 \,\mathrm{uA}$ , considering both power efficiency and area, the optimal value for the capacitance is chosen as  $60 \,\mathrm{pF}$ .

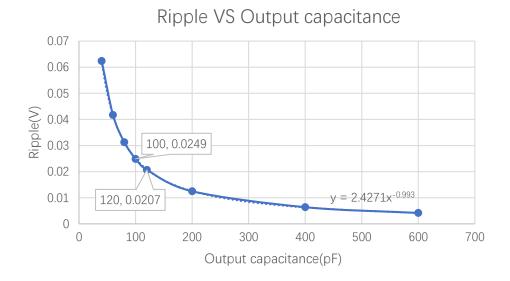

### b) Output capacitance

The output capacitor  $C_L$  is related to ripple. When frequency is fixed,  $C_L$  is inversely proportional to the ripple. When loading current is 1 uA and frequency is at 200 kHz, an output capacitor of 100 pF is selected. At this time, the ripple is 25 mV, which is 1.25% of the output voltage.

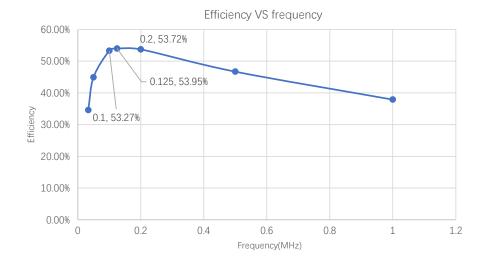

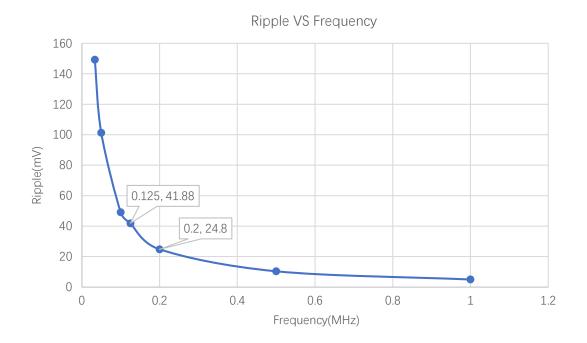

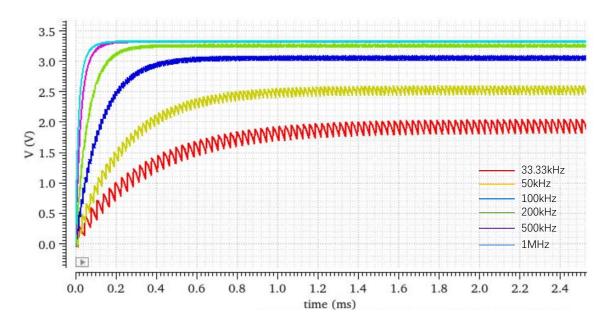

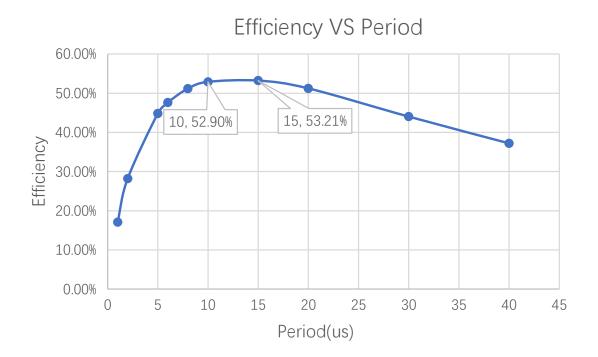

#### D. Frequency choice

Frequency affects efficiency, output voltage ripple, and output current of the circuit. The efficiency of the charge pump increases with increasing frequency because more charge is transferred per unit time. However, When the frequency increases to a certain value, increasing the frequency will decrease efficiency as the buffer power consumption increases. Frequency at 200 kHz is considered as the optimal frequencies, with a efficiency of 53.72%.

#### E. Power efficiency optimization

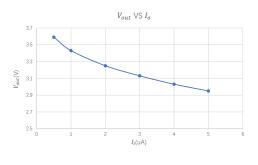

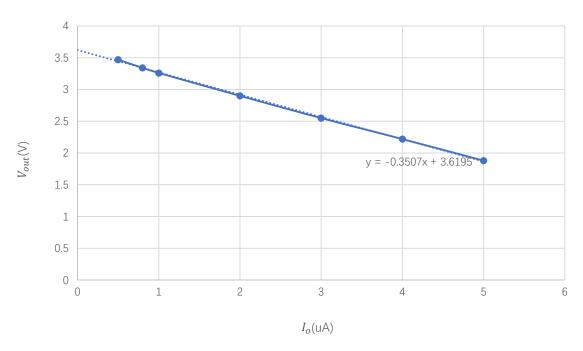

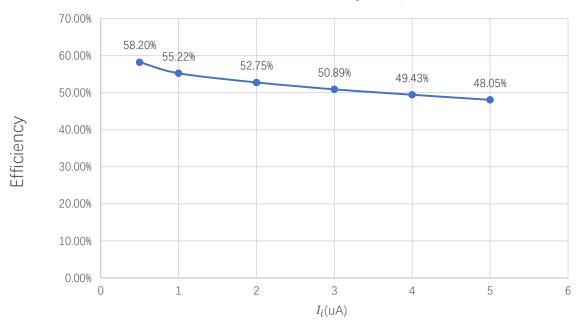

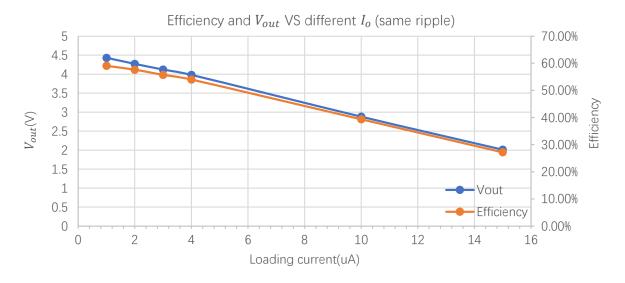

With increasing the loading current while change the frequency to keep ripple constant,  $V_{out}$  will decrease as  $I_o$ increases, shown in Fig. 3, because of the MOSFET size limitations on load current. According to Equation 6, the power efficiency will decrease following the decrease of  $V_{out}$ . Equation 6 is derived by apart the buffer power into two

Fig. 3: Vout VS Io

parts: one part related to the loading current and another part consumed by the parasitic capacitance.

$$\eta = \frac{P_{out}}{P_{in}} = \frac{V_{out} \cdot I_o}{V_{DD} \cdot I_{in} + N \cdot V_{clk} \cdot I_o + C_b \cdot f \cdot V_{clk}^2} \quad (6)$$

where  $C_b$  is the parasitic capacitance in buffer,  $I_{in}$  is the input current, which is equal to  $I_o$ .

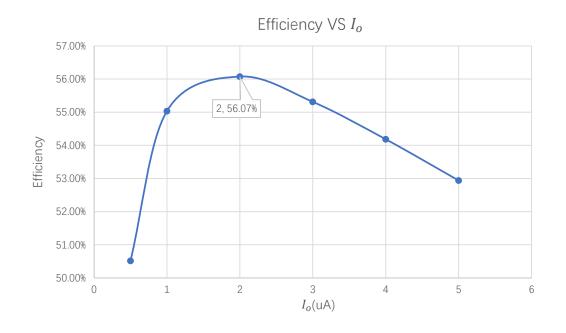

When frequency is fixed and ripple is changed, as  $V_{out}$  can be expressed by  $I_o$  according to Equation 1 and Equation 2. Combine with Equation 6, there will be optimal value of  $I_o$ . From simulation results, the optimal  $I_o$  is 2 uA, with an efficiency of 56.07%.

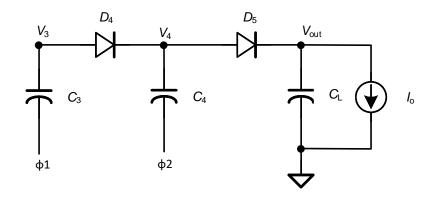

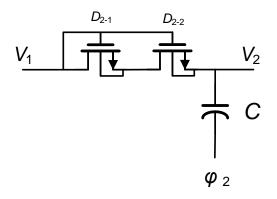

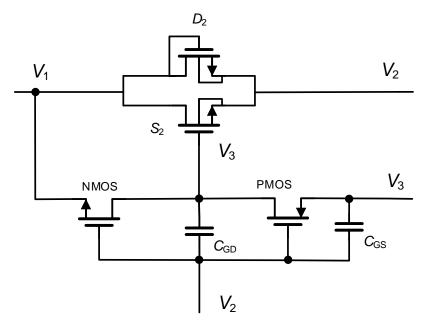

### IV. CHARGE PUMP WITH CHARGE TRANSFER SWITCHES(CTS'S)

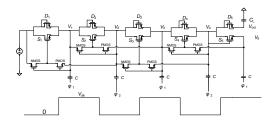

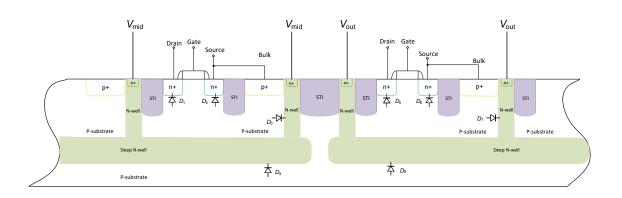

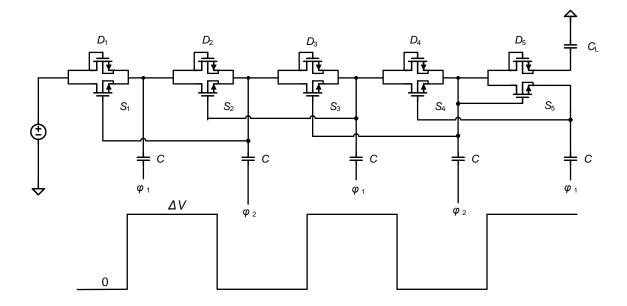

Dickson charge pump has a drawback of  $V_{th}$  loss. In [3] new topology utilizing charge transfer switches is applied, classified into static CTS's and dynamic CTS's. For static CTS's, parallel MOSFET switches are applied to MOSFET

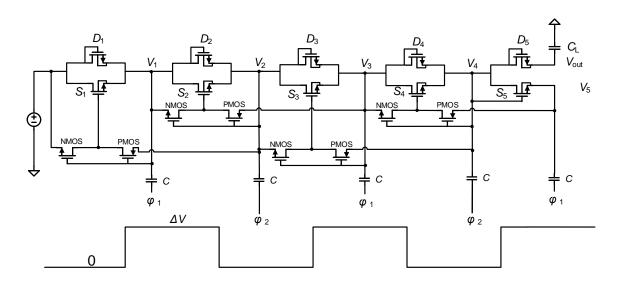

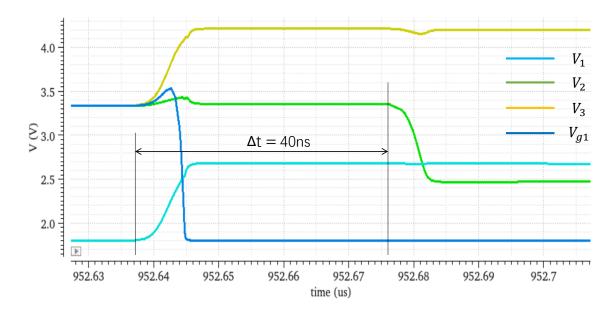

diodes. But as the MOSFET switches is closed all the time, static CTS's has a problem of reverse charge sharing. To solve this problem, inverters are used to control these switches in dynamic CTS's. The schematic of dynamic CTS's charge pump is shown in Fig. 4.

Fig. 4: Schematic of dynamic CTS's charge pump

### A. MOSFET design

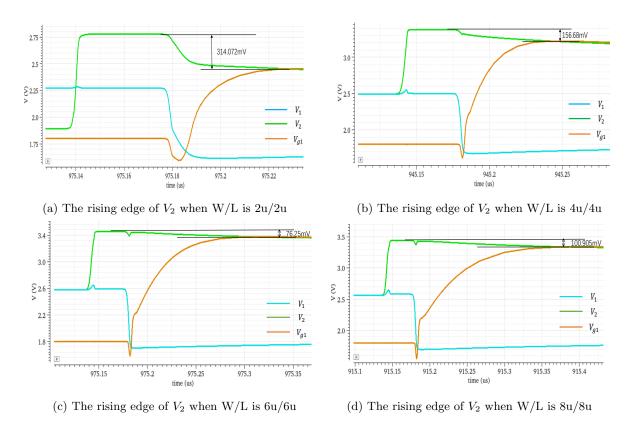

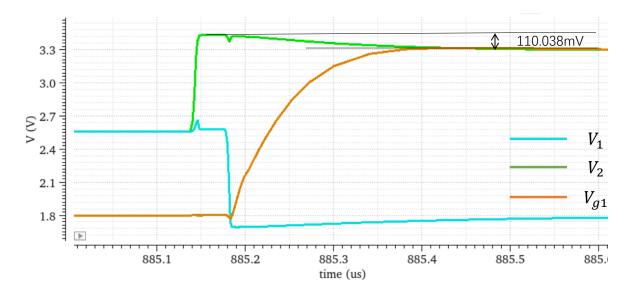

For the design of MOSFET diodes(MD) and switches(MS), same considerations are taken into account as in Dickson charge pump. For the inverter, driving capability of NMOS should be strong to reduce the reverse charging sharing time. And driving capability of PMOS should not be too strong to weak NMOS relatively. The parameters are shown in Table I:

| W/L of MD   | W/L of MS  | W/L of NMOS  | W/L of PMOS    |

|-------------|------------|--------------|----------------|

| 20 um/ 8 um | 2 um/ 6 um | 8 um/ 200 nm | 1.335 um/ 8 um |

TABLE I: MOSFETs size in Dynamic CTS's

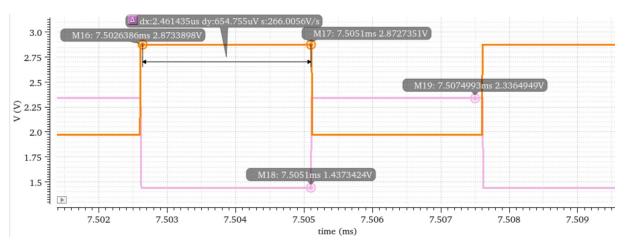

#### B. Capacitance size and frequency choice

The design of capacitors and frequency is similar to the situation in Dickson charge pump. The optimal value of the capacitor is 100 pF.And the optimal frequency is chosen as 100 kHz. For  $C_L$ , to maintain a ripple of 25 mV, the chosen value is 200 pF.

#### C. Power efficiency optimization

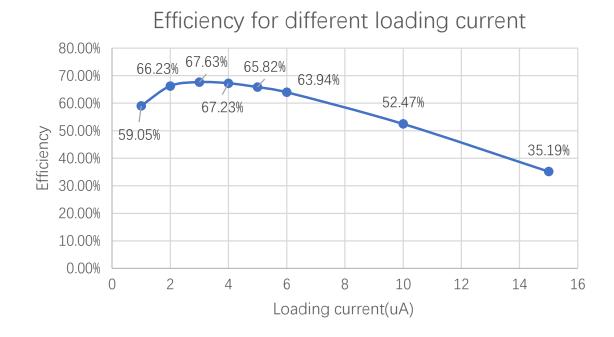

Efficiency varies with loading current and the maximum efficiency can reach 67% when the load is 3 uA, whereas the efficiency drops to only 35% when the load is 15 uA.

#### V. CONCLUSION

In this thesis, how to generate on-chip high voltage on CMOS device is designed. The objective of this article is to achieve a 20V output using charge pump from a 1.8V supply voltage while simultaneously reducing chip area and improving power efficiency. Dickson charge pump and dynamic CTS's charge pump are designed.

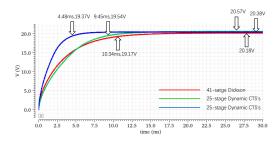

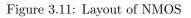

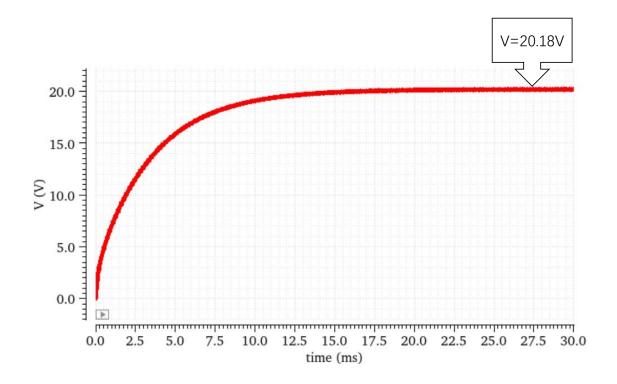

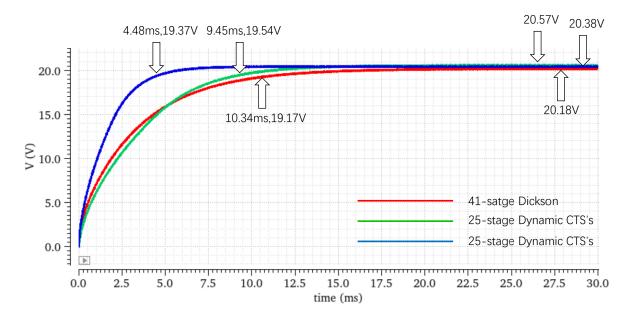

Fig. 5 depicts a comparison of two scenarios when  $V_{out}$  is 20V. One scenario is when the parameters of the Dickson and dynamic CTS's are set the same, while the other scenario is when the Dickson and dynamic CTS's are set to their respective optimal parameters. The load current is fixed at 1 uA.

Fig. 5: Comparison of three situations

When all the parameters in Dickson charge pump and dynamic CTS's are same, the dynamic CTS's structure can use a smaller size of  $0.285mm^2$  and provide a high power efficiency of 53% to reach the same output voltage of 20V. Also has a lower settling time of 4.48 ms to achieve 95% of 20V. For the respective optimal situation, although larger capacitance and lower frequency can increase the efficiency, more area is required. So design which kind of charge pump is a trade-off between the area and power efficiency. Table II shows simulation results in detail.

|                       | Dickson     | Dynamic CTS's | Dynamic CTS's |

|-----------------------|-------------|---------------|---------------|

| Stages                | 41          | 25            | 25            |

| Vout                  | 20.18V      | 20.38V        | 20.57V        |

| Ripple                | 25mV        | 25mV          | 25mV          |

| Frequency             | 200kHz      | 200kHz        | 100kHz        |

| $C_i$                 | 60pF        | 60pF          | 100pF         |

| $C_L$                 | 100pF       | 100pF         | 200pF         |

| T <sub>settling</sub> | 10.34ms     | 4.48ms        | 9.45ms        |

| Area                  | $0.457mm^2$ | $0.285mm^{2}$ | $0.482mm^2$   |

| Efficiency            | 43.33%      | 53%           | 71.15%        |

TABLE II: Parameters in design

#### ACKNOWLEDGMENT

I would like to express my sincere gratitude to Prof. dr. ir. Guy Torfs and Prof. dr. ir. Johan Bauwelinck, my promotors, for providing me with the opportunity to do this research and for their guidance in my classes throughout the past two years.

I am also indebted to Xin Wang, and Achim Vandierendonck, my supervisors, for their unwavering support and insightful suggestions.

Lastly, I would like to thank my family and friends for their constant encouragement and support.

#### REFERENCES

- M. Innocent, P. Wambacq, S. Donnay, H. A. Tilmans, H. De Man, and W. Sansen, "Mems variable capacitor versus mos variable capacitor for a 5ghz voltage controlled oscillator," in Proceedings of the 28th European Solid-State Circuits Conference, pp. 487–490, IEEE.

- [2] J. F. Dickson, "On-chip high-voltage generation in MNOS integrated circuits using an improved voltage multiplier technique," IEEE J. Solid-State Circuits, vol. 11, pp. 374–378, June 1976.

- [3] J.-T. Wu and K.-L. Chang, "Mos charge pumps for low-voltage operation," IEEE Journal of solid-state circuits, vol. 33, no. 4, pp. 592–597,1998.

This page is intentionally left blank.

### **Table of Contents**

| Ac                     | nowledgements                                                                                                                                                                                                                                                                                                                                                                                                       | $\mathbf{v}$                                                            |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| $\mathbf{Ad}$          | ission to loan                                                                                                                                                                                                                                                                                                                                                                                                      | vii                                                                     |

| $\mathbf{A}\mathbf{b}$ | ract                                                                                                                                                                                                                                                                                                                                                                                                                | ix                                                                      |

| $\mathbf{E}\mathbf{x}$ | nded Abstract                                                                                                                                                                                                                                                                                                                                                                                                       | xi                                                                      |

| Ta                     | e of Contents                                                                                                                                                                                                                                                                                                                                                                                                       | xv                                                                      |

| $\mathbf{Lis}$         | of Figures                                                                                                                                                                                                                                                                                                                                                                                                          | xvii                                                                    |

| $\mathbf{Lis}$         | of Tables                                                                                                                                                                                                                                                                                                                                                                                                           | xviii                                                                   |

| 1                      | ntroduction         1       High voltage application         2       High voltage generation         3       The supply voltage and channel length scaling on CMOS technology         4       Goal of this thesis                                                                                                                                                                                                   | $\begin{array}{ccc} \cdot & \cdot & 1 \\ \cdot & \cdot & 2 \end{array}$ |

|                        | ickson Charge Pump         1 The principle of Dickson charge pump         2 Parameters of Dickson charge pump         2.2.1 Output voltage         2.2.2 Settling time         2.2.3 Ripple         2.2.4 Power Consumption         3 Break down voltage consideration         2.3.1 Break down voltage         2.3.2 DNW connection                                                                                | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                    |

|                        | esign of Dickson Charge Pump         1       Switch design         3.1.1       Length         3.1.2       Width         2       Area limit         3       Power consumption         4       Capacitor size choice         3.4.1       Capacitor in each stage         3.4.2       Output capacitor         5       Frequency choice         6       Power efficiency optimization         7       Issue of Dickson | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                    |

| 4                      | Charge Pump with Charge transfer switches         1       The static CTS's                                                                                                                                                                                                                                                                                                                                          | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                   |

|    |             | PMOS NW connection consideration |    |

|----|-------------|----------------------------------|----|

| 5  | Conclusion  | 1                                | 59 |

| Bi | ibliography |                                  | 61 |

### List of Figures

| $1.1 \\ 1.2$ |                                                                                                                                                                                                          | 2<br>3 |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 2.1          | Schematic of 4-stage Dickson charge pump without loading                                                                                                                                                 | 5      |

| 2.2          | Charge transfer process in the first stage                                                                                                                                                               | 6      |

| 2.3          | The first method to calculate transferred charge                                                                                                                                                         | 6      |

| 2.4          | The second method to calculate transferred charge                                                                                                                                                        | 9      |

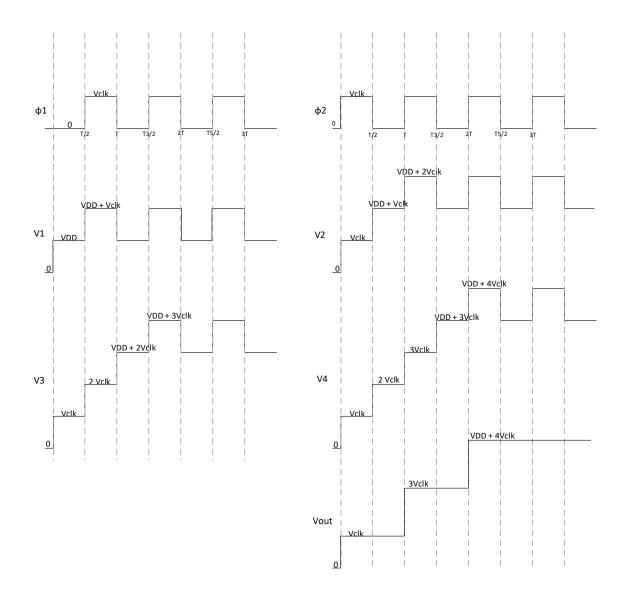

| 2.5          | Dynamic process of $V_1$ to $V_4$ and $V_{out}$ ignoring Vth                                                                                                                                             | 1      |

| 2.6          | Dynamic process of $V_1$ to $V_4$ and $V_{out}$ considering Vth $\ldots \ldots \ldots$   | 2      |

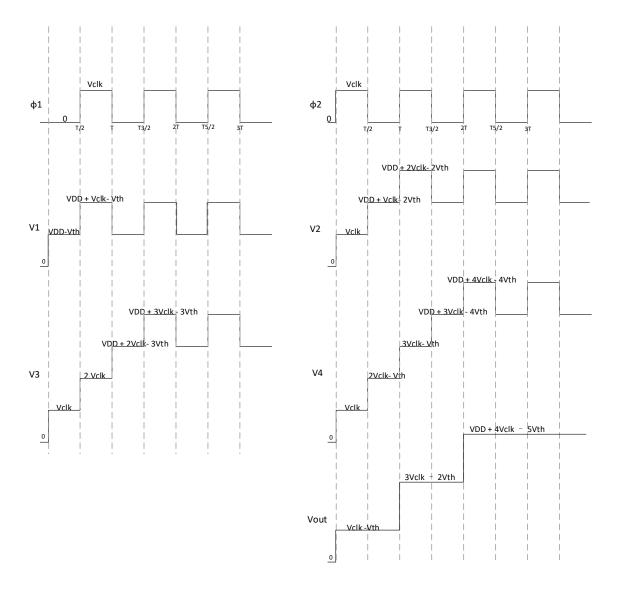

| 2.7          | Part of the schematic of a 4-stage charge pump with loading current 13                                                                                                                                   | 3      |

| 2.8          | Figure of $V_4$ and ripple                                                                                                                                                                               | 4      |

| 2.9          | Cross-section of NMOS transistor layout in deep N-well 10                                                                                                                                                | 6      |

| 2.10         | Breakdown voltage limitation                                                                                                                                                                             | 7      |

|              | DNW connection                                                                                                                                                                                           | 7      |

| 3.1          | Structure of the second stage in Dickson charge pump                                                                                                                                                     | C      |

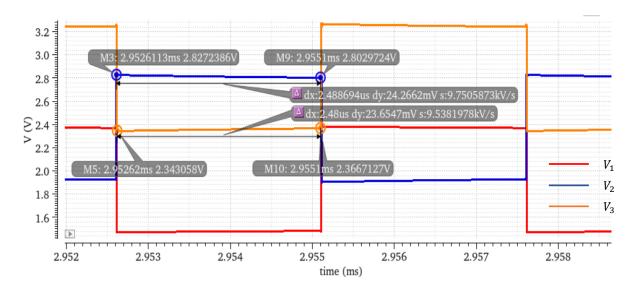

| 3.2          | Channel length is 4 um with a width of 1 um $\ldots \ldots 20$                                                                     | )      |

| 3.3          | Channel length is $6 \text{ um}$ with a width of $1.5 \text{ um}$ $\ldots \ldots \ldots \ldots \ldots \ldots 2$                                                                                          | 1      |

| 3.4          | $V_{out}$ VS channel length                                                                                                                                                                              | 2      |

| 3.5          | $V_1(\text{pink})$ and $V_2(\text{orange})$ in steady state without load                                                                                                                                 | 2      |

| 3.6          | $V_3$ (green) and $V_4$ (blue) in steady state without load $\ldots \ldots \ldots$       | 3      |

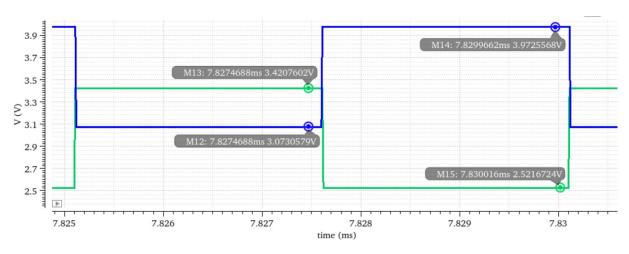

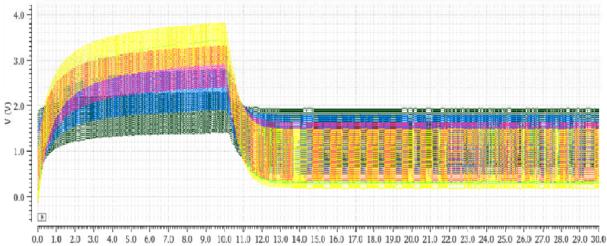

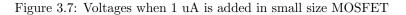

| 3.7          | Voltages when 1 uA is added in small size MOSFET 23                                                                                                                                                      | 3      |

| 3.8          | $V_1$ when 1 uA is added in small size MOSFET                                                                                                                                                            | 3      |

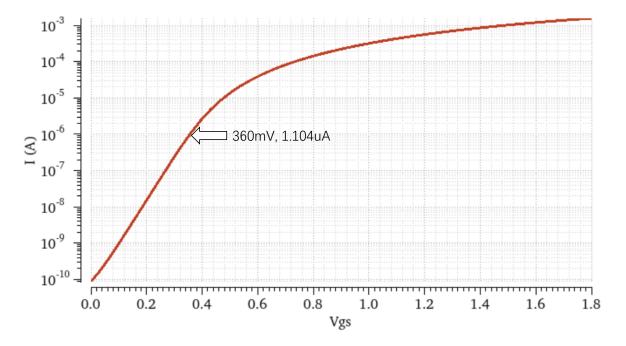

| 3.9          | $I_D \text{ VS } V_{th}$                                                                                                                                                                                 | 4      |

| 3.10         | $V_{out}$ VS channel width of transistors                                                                                                                                                                | 5      |

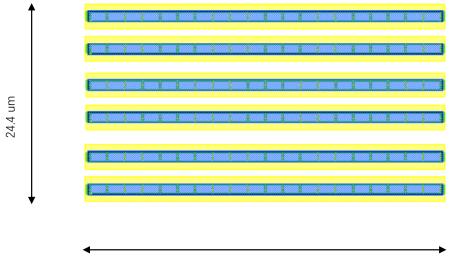

| 3.11         | Layout of NMOS                                                                                                                                                                                           | 6      |

| 3.12         | Layout of buffer                                                                                                                                                                                         | 6      |

| 3.13         | Layout of capacitor                                                                                                                                                                                      | 7      |

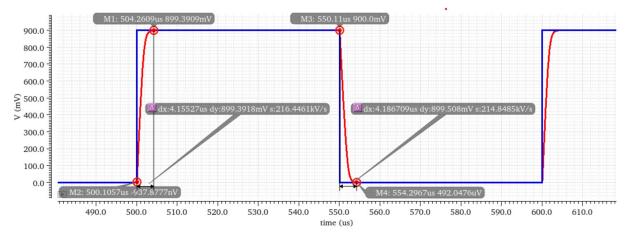

| 3.14         | Test of buffer when load is 1 nF                                                                                                                                                                         | 7      |

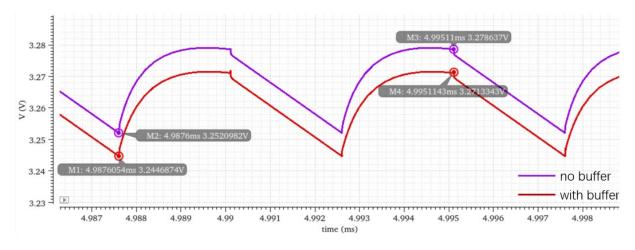

| 3.15         | Vout with buffer and without buffer 22                                                                                                                                                                   | 3      |

|              | Area VS $C_i$                                                                                                                                                                                            | 9      |

| 3.17         | $V_{out}$ of 41-stage charge pump                                                                                                                                                                        | 0      |

| 3.18         | Area/cap density VS small $C_i$                                                                                                                                                                          | 0      |

|              | Area/cap density VS big $C_i$                                                                                                                                                                            | 1      |

|              | Efficiency VS $C_i$ when $I_o$ is 1 $\mu$ A                                                                                                                                                              | 2      |

|              | Ripple VS output capacitor                                                                                                                                                                               | 3      |

|              | Efficiency VS frequency                                                                                                                                                                                  |        |

| 3.23         | Ripple VS frequency                                                                                                                                                                                      |        |

| 3.24         | Settling time with different frequencies                                                                                                                                                                 | 5      |

|              | Efficiency VS $C_i$ for different $I_o$                                                                                                                                                                  |        |

|              | $V_{out}$ with different $I_o$                                                                                                                                                                           |        |

|              | Maximum efficiency VS $I_o$ with fixed ripple                                                                                                                                                            |        |

|              | Maximum efficiency VS $I_o$ with fixed frequency                                                                                                                                                         |        |

| 4.1          | Schematic of charge pump with static CTS's                                                                                                                                                               | 9      |

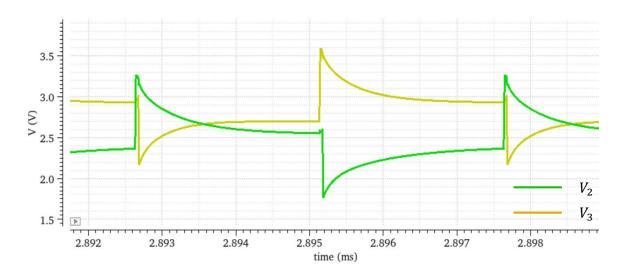

| 4.2          | Voltages of charge pump with static CTS's 44                                                                                                                                                             | )      |

| 4.3          | MS is on                                                                                                                                                                                                 | 1      |

| 4.4          | Simulation results of $V_2$ and $V_3$ in static CTS's charge pump $\ldots \ldots \ldots$ |        |

| 4.5          | Schematic of dynamic CTS's charge pump                                                                                                                                                                   |        |

| 4.6          | Two states of the second stage                                                                                                                                                                           |        |

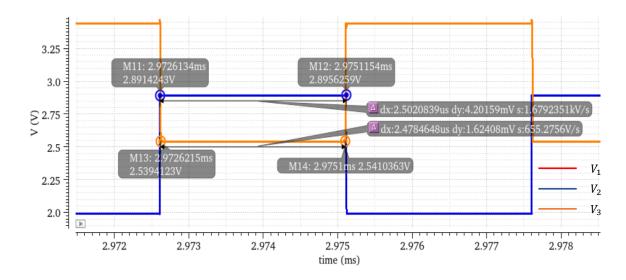

| 4.7  | $V_{out}$ VS channel length of MOSFET diode                                                                                                                                         | 43 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.8  | Vout VS channel width of MOSFET diode with a length of 8 um                                                                                                                         | 44 |

| 4.9  |                                                                                                                                                                                     | 45 |

|      |                                                                                                                                                                                     | 46 |

| 4.11 | $V_{out}$ VS channel length of MOSFET switch $\ldots \ldots \ldots$ | 46 |

| 4.12 | $V_{out}$ VS channel width of MOSFET switch with a length of 6 um                                                                                                                   | 47 |

|      |                                                                                                                                                                                     | 47 |

|      |                                                                                                                                                                                     | 48 |

|      |                                                                                                                                                                                     | 49 |

| 4.16 | Large and small size of NMOS in inverter                                                                                                                                            | 49 |

|      |                                                                                                                                                                                     | 50 |

|      | v                                                                                                                                                                                   | 51 |

|      |                                                                                                                                                                                     | 51 |

|      |                                                                                                                                                                                     | 52 |

|      |                                                                                                                                                                                     | 53 |

| 4.22 | Efficiency VS T                                                                                                                                                                     | 54 |

|      |                                                                                                                                                                                     | 54 |

| 4.24 | Efficiency VS $I_0$                                                                                                                                                                 | 55 |

| 4.25 | Layout of PMOS                                                                                                                                                                      | 55 |

| 4.26 | Comparison of three situations                                                                                                                                                      | 57 |

### List of Tables

|     | $V_{out}$ VS different values of width $\ldots$ Parameters designed in Dickson charge pump $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ |    |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | Parameters in Dynamic CTS's                                                                                                                               |    |

|     | Comparison of 4-stage Dickson and Dynamic CTS's                                                                                                           |    |

| 4.3 | Comparison of 20V in Dickson and Dynamic CTS's                                                                                                            | 56 |

# 1

### Introduction

This chapter covers general conception of high voltage applications, how the high voltage can be generated, The supply voltage and channel length scaling on CMOS technology and the goal of this thesis.

### 1.1 High voltage application

High voltage, which exceeds the maximum supply voltage of sub-micron CMOS technology, is now being increasingly applied in various electronic systems. In nonvolatile memories like EEPROM and flash memory, high voltage is required for programming or erasing on the chip[1]. In radio frequency identification (RFID) systems, high voltage is needed to drive the memory module in the tag to record product information data[2]. In MEMS systems, variable capacitors (such as MOS or PN junction capacitors) are utilized to enhance the linearity of tunable RF filters[3] or improve the phase noise of voltage-controlled oscillators[4]. However, achieving the desired performance of these variable capacitors often requires high-voltage power supplie[5]. In addition, for measuring the acoustic ringing effect of electro-optic (EO) crystals, a high voltage square pulse with fast response is required. This is essential to accurately analyze and characterize the behavior of the EO crystal under acoustic excitation[6]. Besides, high voltage is applied in nematic liquid-crystal (NLC) devices to rapidly drive the molecular director, reducing the required time for state transitions[7].

### 1.2 High voltage generation

In the realm of electronic circuit applications, there exists a prevalent need to fulfill high voltage requirements. To address this demand, several commonly employed methods are employed, each designed to achieve the desired voltage levels while adhering to established industry standards and safety protocols. Five methods are discussed below:

**External power supplies** This way is the most easy way to supply voltage. However, in order for CMOS to withstand high voltages, specific process technologies are required, which can lead to increased costs and limitations on the maximum achievable voltage. For example, one dedicated technology Alcatel Mietec HBIMOS allows CMOS sections to operate up to 15V[8].

**Boost Chopper** The Boost circuit is based on the principle of utilizing an inductor and a switch element (such as a MOSFET) to periodically switch and interrupt the circuit in order to convert electrical energy. It is commonly used for increasing the output voltage from a lower input voltage level. The Boost circuit is suitable for applications where high output voltage is required, but it is more applicable to scenarios with relatively larger current requirements.

**Charge pumps** Charge pump is a DC-DC converter that converts low voltage to high voltage. But unlike the common BOOST circuit, the charge pump does not require inductive components, it only consists of switches and capacitors. Each stage is composed of a switch (MOSFET or diode) and a capacitor in series. They are efficient and compact solutions for boosting voltage levels.

**Voltage multipliers** Voltage multiplier circuits, such as Cockcroft-Walton multipliers[9], can generate higher voltages by using a series of capacitors and diodes to multiply the input voltage. Voltage Multiplier cell can also be integrated with windings to work as a high step-up nonisolated dc–dc converter to achieve high voltage conversion ratio[10].

**Transformers** A transformer can convert input voltage to a higher voltage through magnetic coupling. By adjusting the turns ratio of the transformer, different output voltages can be achieved.

Applying external voltages imposes higher process requirements and costs. Compared to voltage multipliers and high-voltage integrated circuits (HVICs), charge pumps provide more controllable outputs, which can be adjusted by tuning the frequency, stages, and capacitance values. Furthermore, charge pump circuits consist only of CMOS and capacitors in series, resulting in a simple structure without external components and achieving a higher level of integration. And the most importantly, Charge pumps are widely used for low supply voltage situations.

### 1.3 The supply voltage and channel length scaling on CMOS technology

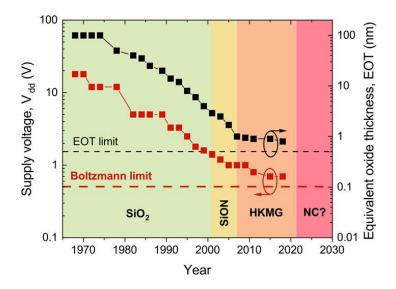

Figure 1.1 illustrates the trend of supply voltage  $V_{DD}$  and Equivalent Oxide Thickness(EOT) over the past 50 years. As the size of EOT continues to decrease, the voltage drop across the gate oxide layer reduces to improve the reliability of the transistor. On the other hand, the scaling down on voltage brings a power consumption reduction for digital intensive circuit in advanced nano CMOS technology.

Figure 1.1: Historic trend of supply voltage [11]

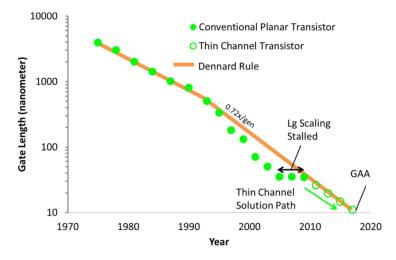

Figure 1.2 indicates the historic trend of gate length from 1970 to 2020. In 2009, 28 nm can already be implemented. Gate length has been a critical parameter in driving the advancements in integration technology, playing a pivotal role in improving performance, packing density, power efficiency, and transistor cost. A lower nanometer process technology offers higher integration, lower power consumption, and improved performance. However, smaller gate length poses challenges related to complexity, cost, yield, reliability, design, and timing. In this dissertation, 28 nm CMOS devices are applied.

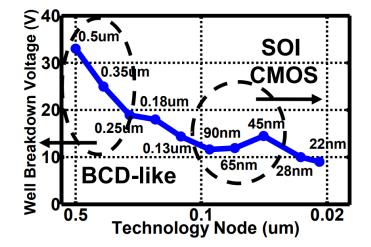

Figure 1.1 and Figure 1.2 pose three major challenges for a charge pump design. Firstly, the small break down voltage of the transistor requires careful design both in schematic and layout to avoid any potential reliability issue. Secondly, the low available voltage in advanced CMOS technology require more stages to achieve the largest output voltage at the spend of more chip area and higher power consumption. Thirdly, the short channel length addresses a large leakage when a transistor is at 'off' state, ultimately resulting a large area design since minimum channel length choice is impossible.

Figure 1.2: Historic trend of gate length [12]

illustrate a clear trend in the field, wherein the pursuit of small area and low power consumption is prominent. To achieve this, the implementation of charge pumps with a simplistic structure, compact area, and high voltage output is becoming increasingly prevalent. By utilizing low DC voltages, such charge pumps offer a viable solution that finds widespread adoption in various applications.

### 1.4 Goal of this thesis

The objective of this paper is to design a charge pump structure that achieves an output voltage conversion from a 1.8V low-voltage DC power supply to a 20V high-voltage DC output. The analysis focuses on the system's area occupancy and power consumption when applying loading currents. The charge pump structures considered include the Dickson charge pump[13], charge pumps utilizing charge transfer switches (CTS)[1], boost-trap structures[14], series-parallel charge pumps, and charge pumps with adaptive number of stages[15]. This paper primarily focuses on the design, analysis, and comparison of the Dickson charge pump and charge pump structures utilizing CTS.

Chapter 2 introduces the basic principles of the Dickson charge pump and the parameters to consider during its design. Chapter 3 discusses how to design the Dickson charge pump and limitations of Dickson charge pump. Chapter 4 presents the principles and design of two kinds of charge pumps utilizing charge transfer switches, which are static CTS's and dynamic CTS's respectively. And a comparative analysis of the Dickson charge pump and the dynamic CTS charge pump in terms of output, load, area, and power consumption is provided. This page is intentionally left blank.

### **Dickson Charge Pump**

### 2.1 The principle of Dickson charge pump

To understand how Dickson charge pump works, consider a 4-stage charge pump shown in Figure 2.1.

Figure 2.1: Schematic of 4-stage Dickson charge pump without loading

Circuit is supplied by a low DC voltage of 1.8 Volt.  $V_1$  to  $V_4$  refers to nodes voltages. For each stage, diode works as a switch, and a capacitor is used to store and release charges when switch is on and off. One end of the two sides of capacitor is connected to the diode, and the other end is connected to the clock pulse. All the odd-donated stages are controlled by  $\phi_1$ , all even-donated stages are controlled by  $\phi_2$ . The phase difference of  $\phi_1$  and  $\phi_2$  is 90 degrees. The state of the switches are controlled by these two out-of-phase clock phases. The output capacitor after the last stage is connected to ground instead of clock signal, acting as a low-pass filter together with the last switch. This filter suppresses the influence of the high-frequency response of the output clock on the output voltage, in other words, output capacitor can reduce the ripple[16].

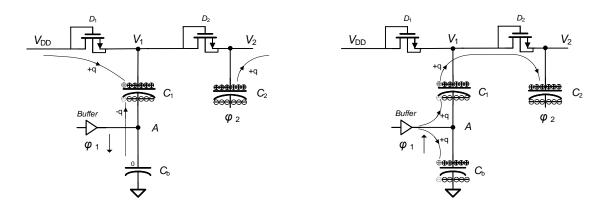

Figure 2.2 indicates the process of charge transfer in the first stage. The clock voltage flows into the circuit after passing through the buffer, where  $C_b$  is the parasitic capacitance on the buffer.

- When  $\phi_1$  is low, the process is shown in Figure 2.2a. The voltage at point A is 0, and the charge on the upper and lower plates of  $C_b$  is 0. At this time,  $D_1$  is turned on, source voltage charges  $V_1$ , and the positive charge flows from  $V_{DD}$  to  $V_1$ . The upper plate of capacitor  $C_1$  experiences an increase in positive charge, resulting in the subsequent flow of negative charge from the ground towards the lower plate of  $C_1$ , thereby allowing for the accumulation and storage of charge within  $C_1$ .

- When  $\phi_1$  is high, the positive charge from buffer flows to the lower plate of  $C_1$ . The positive charge counteracts the negative charge residing on the lower plate, facilitating the transfer of positive

charge from the upper plate of  $C_1$  through diode  $D_2$  to the next stage. At the same time, the buffer charges the  $C_b$ , and the positive charge flows to the upper plate of the  $C_b$ .  $C_b$  also consumes power, which will be discussed in power consumption section later.

(b) Charge transfer of  $V_1$  when  $\phi_1$  is high

Figure 2.2: Charge transfer process in the first stage

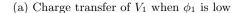

The essential reason why the voltage can be increased is that the charge from the power supply charges the capacitance of each stage. The voltage is increased by controlling the charging and discharging process of the capacitor through the two out-of-phase clock signals. The clock signals are used to control the capacitor to store and release the charge to realize the charging and discharging process, and finally realize the step-by-step increase of the voltage. In [17], the recurrence formula of the output voltage  $V_{out}$ is derived in detail, by obtaining the total consumed charge in two ways. The first way is to calculate the total charge stored in each capacitor. The second way is to calculate the charge transferred in one time cycle, illustrated in figure 2.3 and 2.4 respectively. For the first method, in a N-stage charge pump, define  $Q_{i,j}$  ( $1 \le i \le N$ ) as charge stored in capacitance at  $i^{th}$  stage  $C_i$  at time j, and define the total charge consumed by  $i^{th}$  stage from initial time 0 to time j as  $Q_{DD,i,j}$ , which is the sum of charge transferred to  $C_{i+1}, C_{i+2}, ..., C_N$  and the output capacitance  $C_L$ .  $\Delta Q_i$  is the increased charge in each stage. The process is shown in figure 2.3[17].

Figure 2.3: The first method to calculate transferred charge

To get recurrence formula of the output voltage, the total consumed charge needs to be calculated. Define  $Q_{total}$  as the total charge consumed by the circuits during time j. From Figure 2.3, the charge consumed by the last stage is the charge flowing to the load:

$$Q_{DD,N,j} = Q_{load,j} - Q_{load,0} \tag{2.1}$$

For the  $i^{th}$  stage,

$$Q_{DD,i,j} = \sum_{k=i+1}^{N} (Q_{k,j} - Q_{k,0}) + Q_{load,j} - Q_{load,0}$$

(2.2)

Then the total charge consumed by the whole charge pump circuits:

$$Q_{total} = \sum_{i=0}^{N} Q_{DD,i,j} = \sum_{i=0}^{N} \left[ \sum_{k=i+1}^{N} (Q_{k,j} - Q_{k,0}) + Q_{load,j} - Q_{load,0} \right] = \sum_{k=1}^{N} k(Q_{k,j} - Q_{k,0}) + (N+1)(Q_{load,j} - Q_{load,0})$$

$$(2.3)$$

Define q(j) as the amount of charge flowing from one capacitor  $C_i$  to the next capacitance  $C_{i+1}$  at time j in one clock period. Analyze from the first stage. There are several assumptions that need to be satisfied when analyzing.

- Each MOSFET has constant value of threshold voltage  $V_{th}$  [18].

- The capacitance in each stage  $C_i$   $(1 \le i \le N)$  is identical to each other. And the amount of charge transferred to output stage in steady state is identical to the amount of charge transferred from one stage to the next stage.

- Assume the first diode  $D_1$  is off when t=j.

- Parasitic capacitance is not taken into account.

Then expression of the charge stored in  $C_1$  at time j can be written:

$$Q_{1,j} = C_1 \cdot V_{1,j} = C_1 \cdot (V_{DD} - V_{th}) \tag{2.4}$$

$V_{th}$  is the threshold voltage of diodes and  $V_{DD}$  is the source voltage. When the first stage is charging the second stage, the amount of charge transferred from  $C_1$  to  $C_2$  is q(j). Then the amount of charge remaining on  $C_1$  is  $Q_{1,j} - q(j)$ , and the amount of charge remaining on  $C_2$  is  $Q_{2,j} + q(j)$ . So at time  $j + \frac{1}{2}$ , the voltages at the first stage and the second stage  $V_{1,j+\frac{1}{2}}$  and  $V_{2,j+\frac{1}{2}}$  are shown in Equation 2.5 and Equation 2.6 respectively.

$$V_{1,j+\frac{1}{2}} = \frac{Q_{1,j} - q(j)}{C}$$

(2.5)

$$V_{2,j+\frac{1}{2}} = \frac{Q_{2,j} + q(j)}{C}$$

(2.6)

As the second stage will be charged only when  $\phi_1$  is high, in stead state (at time  $j + \frac{1}{2}$ ), the maximum voltage that the second stage can reach is limited by the threshold voltage. The following equations can be obtained under the condition that the second diode  $D_2$  is off when  $t = j + \frac{1}{2}$ :

$$V_{DD} + V_{1,j+\frac{1}{2}} - V_{2,j+\frac{1}{2}} = V_{th}$$

(2.7)

Combine Equation 2.5, Equation 2.6 and Equation 2.7,  $Q_{2,j}$  can be calculated as :

$$Q_{2,j} = 2C \cdot (V_{DD} - V_{th}) - 2q(j) \tag{2.8}$$

Similarly, the third diode  $D_3$  is off when t = j:

$$V_{DD} + \frac{Q_{2,j}}{C} - \frac{Q_{3,j}}{C} = V_{th}$$

(2.9)

Combine Equation 2.8 and Equation 2.9,  $Q_{3,j}$  can be derived as:

$$Q_{3,j} = 3C \cdot (V_{DD} - V_{th}) - 2q(j) \tag{2.10}$$

Then extend to general expression for N stages. When N is odd,

$$Q_{2k-1,j} = (2k-1) \cdot C \cdot (V_{DD} - V_{th}) - 2(k-1)q(j)$$

(2.11)

When N is even,

$$Q_{2k,j} = 2k \cdot C \cdot (V_{DD} - V_{th}) - 2kq(j)$$

(2.12)

where  $1 \le k \le \frac{N}{2}$ . Consider the case where N is even, the charges stored in the last capacitor  $C_N$  at time j is

$$Q_{N,j} = (N-1) \cdot C \cdot (V_{DD} - V_{th}) - Nq(j)$$

(2.13)

When t = j, the output diode  $D_{N+1}$  is off, so

$$V_{DD} + \frac{Q_{N,j}}{C} - V_{out} = V_{th}$$

(2.14)

Combine Equation 2.13 and Equation 2.14, the amount of charge flowing from one capacitor  $C_I$  to the next  $C_{k+1} q$  can be expressed as:

$$q(j) = \frac{C}{N}((N+1)(V_{DD} - V_{th} - V_{out}))$$

(2.15)

Then the charge stored in each stage is calculated as [18]:

$$Q_{2k-1,j} = \frac{2(k-1)}{N} \cdot C \cdot (V_{out} - (V_{DD} - V_{th})) + C \cdot (V_{DD} - V_{th})$$

(2.16)

$$Q_{2k,j} = \frac{2k}{N} \cdot C \cdot (V_{DD} - V_{th}) \tag{2.17}$$

According to Equation 2.16 and Equation 2.17, assume the initial condition that:  $Q_{2k-1,0} = C(V_{DD} - V_{th})$ ,  $Q_{load,0} = C_{load}(V_{DD} - V_{th})$  and  $Q_{2k,0} = 0$ . Then the total consumed charge can be derived from Equation 2.3 as [17]:

$$Q_{total} = (N+1)C_{out}(V_{out,j} - (V_{DD} - V_{th}))$$

(2.18)

$$C_{out} = C_{load} + A(N)C \tag{2.19}$$

$$A(N) = \frac{4N^2 + 3N + 2}{12(N+1)}$$

(2.20)

$$A(N) = \frac{4N^2 - N - 3}{12N} \tag{2.21}$$

Equation 2.20 and equation 2.21 correspond to the cases where N is even and odd respectively.

Except for calculated the consumed charge in each stage, calculating the consumed charge in one cycle time is also considered. Figure 2.4 indicates how this method works. Define  $q_{DD}(j)$  as the total supplied charge by the source from time j to j+1(during one clock period). Define  $q_{total}(j)$  as the total supplied charge by the source from time 0 to time j. As all charges come from the source,  $q_{DD,j}$  is expressed as:

$$q_{DD}(j) = (N+1)q(j) \tag{2.22}$$

And the total supplied charge during time 0 to j is described as

$$q_{total}(j) = \sum_{n=0}^{j} q_{DD}(j) = \sum_{n=0}^{j} (N+1)q(j)$$

(2.23)

Combine Equation 2.15 and Equation 2.23, the final expression of  $q_{total}(j)$  can be written as:

$$q_{total}(j) = (N+1) \sum_{n=0}^{j} \frac{C}{N} [N(V_{DD} - V_{th}) + V_{DD} - V_{th} - V_{out,n}]$$

(2.24)

Now the total charge consumed by the circuit has been deduced by two methods, which are presented in Equation 2.18 and Equation 2.24 respectively. Combining these two equations, the following expression can be obtained:

$$C_{out}(V_{out}(j) - (V_{DD} - V_{th})) = \sum_{n=0}^{j} \frac{C}{N} [N(V_{DD} - V_{th}) + V_{DD} - V_{th} - V_{out,n}]$$

(2.25)

Figure 2.4: The second method to calculate transferred charge

Then the charge deviation from time j to j+1 is

$$C_{out}(V_{out}(j+1) - V_{out}(j)) = \frac{C}{N} [N(V_{DD} - V_{th}) + V_{DD} - V_{th} - V_{out}(j+1)]$$

(2.26)

As have been assumed before, the initial output voltage is  $V_{DD} - V_{th}$ . So the output voltage at time j is calculated:

$$V_{out}(j) = N(V_{DD} - V_{th}) + V_{DD} - v_{th} - N(V_{DD} - V_{th})\beta^j$$

(2.27)

$$\beta = 1/(1 + \frac{c}{NC_{out}}) \tag{2.28}$$

### 2.2 Parameters of Dickson charge pump

### 2.2.1 Output voltage

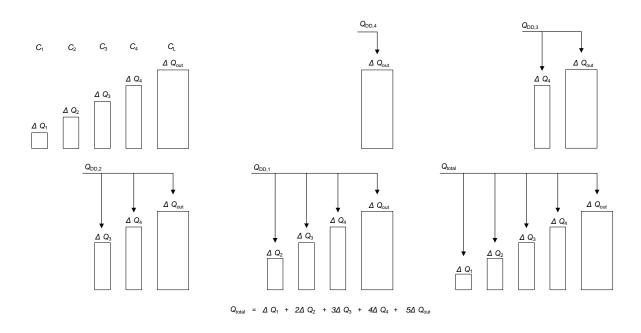

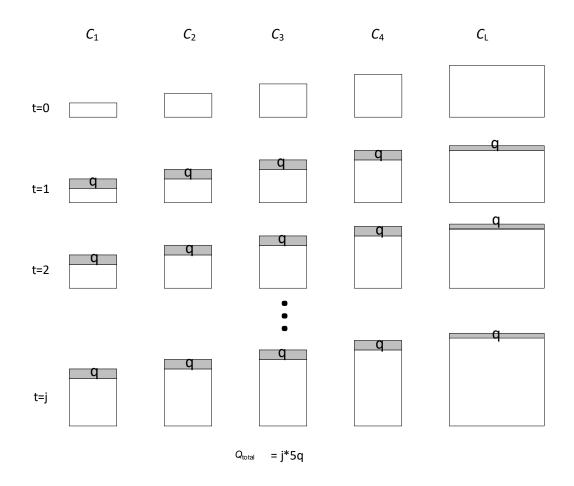

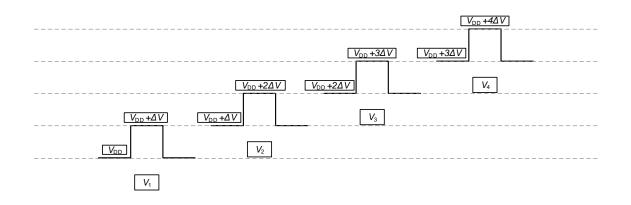

Output voltage is an important parameter to take into account. Consider the same 4-stage charge pump shown in Figure 2.1. Analyze the voltage dynamically. Assume all the initial values of node voltage is 0 V, all the diodes are ideal(threshold voltage of the diode is ignored), and the period of the clock driving the charge pump is significantly greater than the time constants associated with the RC circuit, rendering the RC time constant effects negligible. The dynamic processes of voltage changing is shown in Figure 2.5. Analyze from the first stage again.

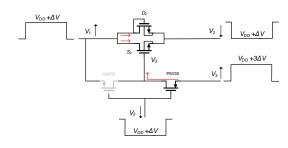

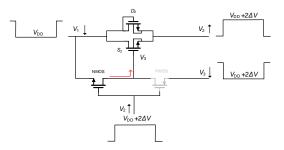

- At time t = 0,  $\phi_1$  is low,  $\phi_2$  is high. The first diode  $D_1$  is turned on and the charge flows from the voltage source to the first capacitance  $C_1$  through  $D_1$ , so the voltage at node 1  $V_1$  will be increased to  $V_{DD}$ . The second diode  $D_2$  and the forth diode  $D_4$  are turned off, and the voltage at node 2  $V_2$  and at node 4  $V_4$  will be increased by the clock pulse to  $V_{clk}$ . The third diode  $D_3$  is turned on, and the voltage at node 3  $V_3$  will be increased to  $V_{clk}$  by charges flowing from the capacitance at second stage  $C_2$ . Diode at output stage  $D_5$  is turned on so the output voltage  $V_{out}$  will be  $V_{clk}$ .

- At time t = T/2,  $\phi_1$  goes from low to high, and  $\phi_2$  goes from high to low.  $D_1$  is turned off and  $V_1$  is increased by the clock pulse to  $V_{DD} + V_{clk}$ .  $D_2$  is turned on. As  $\phi_2$  is low,  $V_2$  will be pulled down by the clock immediately. Because  $V_1$  is larger than  $V_2$ ,  $V_2$  Will be pumped to  $V_1 = V_{DD} + V_{clk}$  in a very short time.  $D_3$  is turned off and  $V_3$  is increased by the clock pulse to  $V_{DD} + V_{clk}$ .  $D_4$  is turned on. The change of  $V_4$  is similar to the process of  $V_2$ .  $V_4$  is pumped to  $V_3 = V_{DD} + V_{clk}$ .  $D_5$  is turned off. The output stage is only charged when the clock of  $N^{th}$  stage is high, so  $V_{out}$  remains at  $V_{clk}$ .

- At time t = T,  $\phi_1$  is low,  $\phi_2$  is high.  $V_1$  is pulled down by the clock to  $V_{DD}$ .  $V_2$  is pulled up by the clock to  $V_{DD} + 2 * V_{clk}$ .  $V_3$  is pulled down by the clock to  $V_{DD}$  and charged by  $C_2$  to  $V_{DD} + 2 * V_{clk}$ .  $V_4$  is pulled up by the clock to  $V_{DD} + 2 * V_{clk}$ . As the last diode is closed, the 4<sup>th</sup> stage will pump the charge to the output stage to increase  $V_{out}$  to  $V_{DD} + 2 * V_{clk}$ .

- At time t = 3T/2,  $\phi_1$  is high, and  $\phi_2$  is low.  $V_1$  is pulled up to  $V_{DD} + V_{clk}$  again. The clock will firstly pull down  $V_2$  to  $V_{DD} + V_{clk}$ . At this moment,  $V_1 = V_2$ , so  $V_2$  will be stable at  $V_{DD} + V_{clk}$ .  $V_3$  is pulled up to  $V_{DD} + 3 * V_{clk}$  and  $V_4$  is charged by  $V_3$  to  $V_{DD} + 3 * V_{clk}$ .  $V_{out}$  remains at  $V_{DD} + 2 * V_{clk}$  as the last switch is open.

- At time t = 2T,  $\phi_1$  is low,  $\phi_2$  is high.  $V_1$  is pulled down by the clock to  $V_{DD}$ .  $V_2$  is pulled up by the clock to  $V_{DD} + 2 * V_{clk}$ . The clock will pull down  $V_3$  to  $V_{DD} + 2 * V_{clk}$ . Since  $V_2$  and  $V_3$  have the same value,  $V_3$  will not be charged. So  $V_3$  remains at  $V_{DD} + 2 * V_{clk}$ .  $V_4$  is pulled up by the clock to  $V_{DD} + 4 * V_{clk}$ . And  $V_{out}$  is charged to  $V_{DD} + 4 * V_{clk}$ .

- At time t = 5T/2,  $\phi_1$  is high, and  $\phi_2$  is low.  $V_1$  is pulled up to  $V_{DD} + V_{clk}$ .  $V_2$  is pulled down to  $V_{DD} + V_{clk}$ .  $V_3$  is pulled up to  $V_{DD} + 3 * V_{clk}$ .  $V_2$  is pulled down to  $V_{DD} + 3 * V_{clk}$ .  $V_{out}$  remains at  $V_{DD} + 4 * V_{clk}$ .

From Figure 2.5, when the threshold voltage of diode is ignored, the first stage will stabilize at  $V_{DD}$  and  $V_{DD} + V_{clk}$ . The second stage will stabilize at  $V_{DD} + V_{clk}$  and  $V_{DD} + 2 * V_{clk}$ . The third stage will stabilize at  $V_{DD} + 2 * V_{clk}$  and  $V_{DD} + 3 * V_{clk}$ . The forth stage will stabilize at  $V_{DD} + 3 * V_{clk}$  and  $V_{DD} + 4 * V_{clk}$ . It can be concluded that the output voltage in stead state is related to the number of stages, the value of voltage supply and the clock voltage. Extend to N stages, the output voltage can be expressed as:

$$V_{out} = V_{DD} + N * V_{clk} \tag{2.29}$$

Figure 2.5: Dynamic process of  $V_1$  to  $V_4$  and  $V_{out}$  ignoring Vth

In practical applications, we usually use a MOSFET, whose gate and drain are connected to act as a diode. During the operation of the charge pump, the threshold voltage  $V_{th}$  of the MOSFET cannot be ignored. The performance of charging in each stage suffers at least a threshold voltage drop in MOSFET. So for the first stage, the stable voltage will be  $V_{DD} - V_{th}$  and  $V_{DD} + V_{clk} - V_{th}$ . The stable voltage of the second stage will be  $V_{DD} + V_{clk} - V_{th}$  and  $V_{DD} + 2 * V_{clk} - 2 * V_{th}$ . The stable voltage at  $V_{DD} + 2 * V_{clk} - 2 * V_{th}$  and  $V_{DD} + 3 * V_{clk} - 3 * V_{th}$ . The forth stage will stabilize at  $V_{DD} + 4 * V_{clk} - 4 * V_{th}$ . And the difference between the  $4^{th}$  stage and the output voltage is also a threshold voltage drop, so the output stage is  $V_{DD} + 4 * V_{clk} - 4 * V_{th} - 5 * V_{th}$ . The waveform of voltage  $V_1$  to  $V_4$  and  $V_{out}$  is shown in Figure 2.6.

Figure 2.6: Dynamic process of  $V_1$  to  $V_4$  and  $V_{out}$  considering Vth

Extend to N stages, the output voltage can be expressed as:

$$V_{out} = V_{DD} + N * (V_{clk} - V_{th}) - V_{th}$$

(2.30)

It's worth mentioning that Equation 2.30 is obtained by assuming each MOSFET has constant values of threshold voltage.

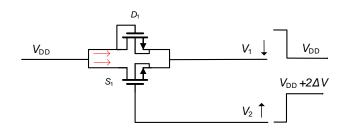

The situation discussed above is where no load is added. It is more realistic to discuss the case of adding load. The schematic of charge pump with load is similar to the schematic of charge pump without load. The only difference is that a current source is added at the output to draw current from the circuit and to act as a load, shown in Figure 2.7.

Figure 2.7: Part of the schematic of a 4-stage charge pump with loading current

Since the topological structure of the intermediate stage in the process of charging and discharging has not changed, the dynamic analysis process after adding a load is the same as when no load is added. Only the voltage pumped to the next stage  $\Delta V$  at the rising edge of the clock changed. When there is no load for the charge pump circuit,  $\Delta V$  is ideally considered to be  $V_{clk}$ . However, in practical,  $\Delta V$  is influenced by  $V_{clk}$ , capacitance in each stage, parasitic capacitance, clock frequency as well as the loading current, which can be expressed as[19]:

$$\Delta V = V_{clk} \cdot \frac{C_i}{C_i + C_p} - \frac{I_o}{f \cdot (C_i + C_p)}$$

(2.31)

where  $V_{clk}$  is the high voltage of the clock pulse,  $C_i$  is the capacitor in each stage,  $C_p$  is parasitic capacitance,  $I_o$  is the loading current and f is the frequency of clock pulse. In this dissertation, the parasitic capacitance is temporarily ignored, so the expression of  $\Delta V$  can be written as

$$\Delta V = V_{clk} - \frac{I_o}{f \cdot C_i} \tag{2.32}$$

Analyze the charging and discharging process as in the previous section, the expression of  $N^{th}$  stage and output voltage can be derived as

$$V_N = V_{DD} - N * (\Delta V - V_{th}) \tag{2.33}$$

$$V_{out} = V_{DD} - N * (\Delta V - V_{th}) - V_{th}$$

(2.34)

Since  $\Delta V$  is smaller than  $V_{clk}$ , the voltage can be pumped each stage is lower. To get the same output voltage, more stages are needed.

### 2.2.2 Settling time

From Figure 2.6, we can not only draw the conclusion that the output voltage is related to the number of stages, but also can see from the figure that the time required for each stage voltage to reach a stable state is different. With i  $(1 \le i \le N)$  increasing, the time increased. And for the output stage, the time needed to get a stable voltage is called settling time. As analyzed in Equation 2.27, it takes time j for the output voltage to increase from  $V_{DD} - V_{th}$  to  $V_{out,j}$ . When the needed output voltage is defined as  $V_{PP}$ , then settling time  $T_{settling}$  is calculated:

$$V_{PP} = (N+1)(V_{DD} - V_{th}) - N(V_{DD} - V_{th})\beta^{T_{settling}}$$

(2.35)

$$T_{settling} = \frac{ln[\frac{(N+1)(V_{DD} - V_{th}) - V_{PP}}{N(V_{DD} - V_{th})}]}{ln\beta}$$

(2.36)

with  $\beta = 1/(1 + \frac{c}{NC_{out}})$ ,  $C_{out}$  is calculated in Equation 2.20 and Equation 2.21.

### 2.2.3 Ripple

As a switching power supply, charge pump circuits introduce system noise that can be fatal to state-ofthe-art data converters, RF radios, phase-locked loops, etc[20]. To suppress noise, low dropout (LDO) regulator is normally cascaded to the switched supply. And providing low output ripple voltage from the charge pump is a feasible method to suppress the noise[20]. In addition, a big output ripple may impact the stability of RRAM write performance[21]. Hence, allowable voltage drop(ripple) is necessary in power supply design.

In Figure 2.6, the output voltage of Dickson charge pump keeps constant in stead state when no load current is added. However, after adding a load current, the output voltage is not a constant value, but changes with the rising and falling edges of the clock. Figure 2.8 shows the changes of output voltage and  $4^{th}$  stage voltage  $V_4$  in one period when charge pump has reached steady state.

Figure 2.8: Figure of  $V_4$  and ripple

In Figure 2.8, one period is divided into two part, half of the period is the blocking time and another half of the period is pumping time. When the clock of the last stage is low, the output voltage is at blocking time. The output capacitor is discharged by the loading current, so the output voltage will go down; When the clock of the last stage is high, the output voltage is at pumping time. The output capacitor is charged by the capacitor in last stage, then the output voltage will go up. The deviation of the voltage during the discharging process(also the charging process) is the ripple. As the amount of the transferred charge is equal, the ripple of the output voltage is given by

$$rippple = \frac{I_o \cdot \Delta t}{C_L} = \frac{I_o}{2 \cdot f \cdot C_L}$$

(2.37)

where  $I_o$  is the loading current,  $\Delta t$  is time of charging or discharging, which is half of the clock period here, and  $C_L$  is the load capacitor at output node. Although its average value of output voltage does not vary with load current, from Equation 2.37, we can know that deviation of output voltage is determined by the loading current, the frequency as well as the output capacitor. To reduce the ripple, lower loading current, larger clock frequency and larger output capacitance is required. To reduce ripple means to minimize the voltage deviation. During the blocking time, the voltage drop is incurred due to charge loss.

$$\Delta V = \frac{I_o}{C_L} \cdot t \tag{2.38}$$

So there are three ways to reduce the voltage drop. Decrease the loading current, increase the load capacitance and increase the clock frequency. The first two methods are to reduce the slope of the V-t curve, so that the charge will be lost less in the same time. The last method is to discharge less time. So the total lost charge  $q = I_o \cdot t$  is lower.

For a given value of ripple, decreasing clock frequency means increasing the output capacitor if the loading current is fixed (1uA). Once frequency is determined, output capacitor can be calculated by Equation 2.37; vice versa. Larger output capacitor leads to larger area, which will increase the cost. However, at the same time, larger output capacitor also means smaller frequency, leading to lower power consumption. At the opposite site, smaller output capacitor means larger frequency, leading to more power consumption and incomplete charge transfer. So the design of load capacitance, load current, and clock frequency are closely related to each other. How to choose the specific value should be traded off according to the system design requirements.

### 2.2.4 Power Consumption

In a charge pump, the power consumption mainly occurs during the switching cycles of the charge pump circuit. Specifically, power is consumed during the charging and discharging of the capacitors in the charge pump circuit. During the charging cycle, the capacitors are charged up to the desired voltage level by drawing current from the power source. During the discharging cycle, the capacitors discharge and provide current to the load. For a realistic charge pump circuit, power current consists of two parts. One part is the current consumption in a ideal charge pump at steady stage  $I_{ideal}$  and another part is due to parasitic effects  $I_{parasitic}$ .

$$I_{power} = I_{ideal} + I_{parasitic} \tag{2.39}$$

As the charge provided by the voltage source is transferred to the load stage by stage,  $I_{ideal}$  can be expressed as [22]:

$$I_{ideal} = (N+1)I_o \tag{2.40}$$

And the parasitic capacitors cause the nonideal part. In the process of charging and discharging, the parasitic capacitance of the upper and bottom plates of the capacitors of each stage C(i) require current. But because the parasitic capacitance value of the bottom board is much larger than other capacitance values. Therefore, approximately the bottom plate capacitance can be considered as the parasitic capacitance is proportional to the value of C(i), the parasitic current can be expressed as[23]:

$$I_{parasitic} = NC_p f V_{clk} = \alpha N C f V_{clk} \tag{2.41}$$

where  $\alpha$  is the ratio of parasitic capacitance of a stage capacitance to stage capacitance, N is number of stages, C is the stage capacitance, f is the clock frequency and  $V_{clk}$  is the clock voltage. So the power consumption can be expressed as:

$$P = I_{power} * V_{clk} = \left[ (N+1)I_o + \alpha NCfV_{clk} \right] * V_{clk}$$

$$\tag{2.42}$$

Conclusion comes out that power consumption of the charge pump circuit is related to the number of stages, the total capacitance, the loading current, the frequency as well as the clock voltage. Combine Equation 2.34, Equation 2.39 and Equation 2.41, substituting the capacitance value with other parameters, the final expression can be derived as:

$$I_{power} = (N+1)I_o + \alpha \frac{N^2}{NV_{clk} + V_{DD} - V_{out}} V_{out}I_o$$

(2.43)

### 2.3 Break down voltage consideration

### 2.3.1 Break down voltage

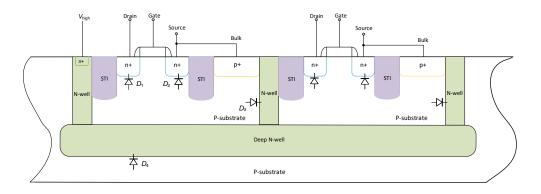

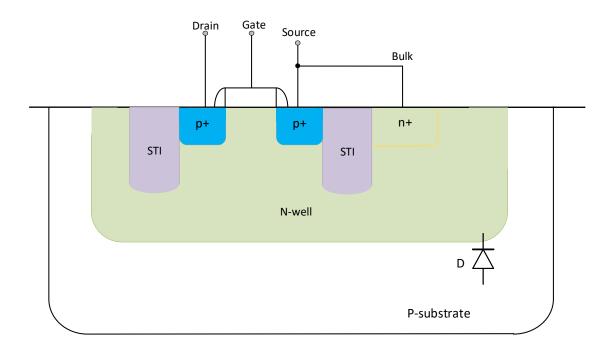

There are several techniques available to ensure the normal operation of CMOS devices under high voltage conditions. While advanced nanoscale CMOS technology offers significant advantages in terms of area and power compared to other technologies like multichip solutions, or exotic technologies(e.g., silicon on insulator (SOI) and Bipolar-CMOS-DMOS) [24], it poses a challenge in terms of reduced voltage tolerance. The cross-sectional view of a standard triple-well CMOS process are shown in the Figure 2.9.

During the design process, it is necessary to satisfy two constraints:

Figure 2.9: Cross-section of NMOS transistor layout in deep N-well

- Preventing forward biasing of the diode.

- Preventing the reversed bias voltage across the diode from exceeding the breakdown voltage.

The tolerance voltage of CMOS is the breakdown voltage of substrate diodes. Then the diode that needs to withstand the highest voltage needs to be found, which determines the breakdown voltage of the process.

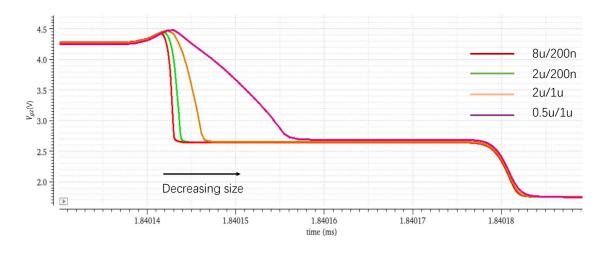

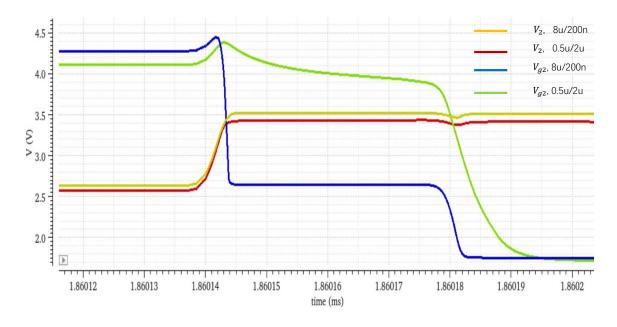

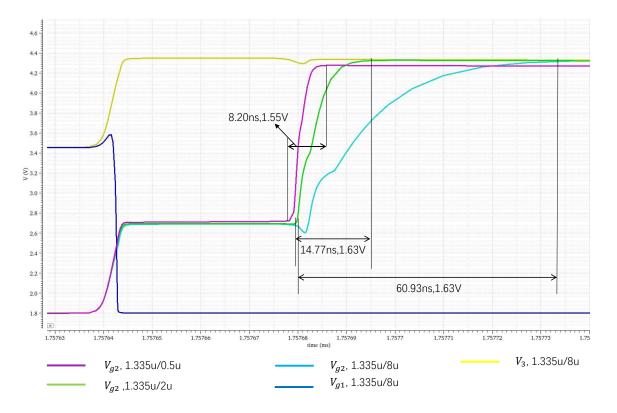

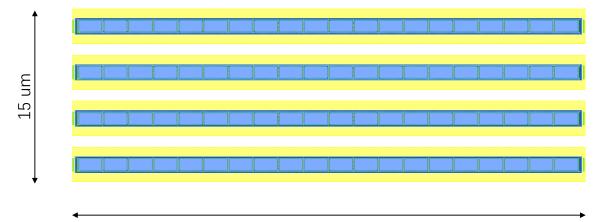

In Figure 2.9, the bulk and source terminals are shorted to prevent back-gate bias effects. And each cell is isolated by N-well. 'Deep Nwell' is a method of isolation that can be employed for NMOS transistors in a PSUB (P-substrate) process. This method involves creating a deep nwell at the bottom and surrounding it with an nwell to form a ring, thereby isolating the transistor from noise interference caused by the common substrate and also improving device speed. If each cell is not separated by N-well, it means that all the bulk connections are joined together, and the buck is connected to the source of the last NMOS. As a result, the p-substrate becomes a high voltage, causing forward biasing of  $D_2$ , preventing the output voltage from reaching the expected value. So N-well is applied to separate each cell.